# McKinsey on Semiconductors

Creating value, pursuing innovation, and optimizing operations

*McKinsey on Semiconductors* is written by experts and practitioners in McKinsey & Company's Semiconductors Practice along with other McKinsey colleagues.

To send comments or request copies, email us: McKinsey\_on\_Semiconductors@ McKinsey.com.

Cover image: © scanrail/Getty Images

#### **Editorial Board:**

Ondrej Burkacky, Peter Kenevan, Abhijit Mahindroo

Editor: Eileen Hannigan

Art Direction and Design: Leff Communications

**Data Visualization:** Richard Johnson, Jonathon Rivait

Managing Editors: Heather Byer, Venetia Simcock

#### **Editorial Production:**

Elizabeth Brown, Roger Draper, Gwyn Herbein, Pamela Norton, Katya Petriwsky, Charmaine Rice, John C. Sanchez, Dana Sand, Sneha Vats, Pooja Yadav, Belinda Yu

#### **McKinsey Practice Publications**

**Editor in Chief:** Lucia Rahilly

**Executive Editors:** Michael T. Borruso, Bill Javetski, Mark Staples

Copyright © 2019 McKinsey & Company. All rights reserved.

This publication is not intended to be used as the basis for trading in the shares of any company or for undertaking any other complex or significant financial transaction without consulting appropriate professional advisers.

No part of this publication may be copied or redistributed in any form without the prior written consent of McKinsey & Company.

### Table of contents

### What's next for semiconductor profits and value creation?

Semiconductor profits have been strong over the past few years. Could recent changes within the industry stall their progress?

#### How will changes in the automotive-component market affect semiconductor companies?

The rise of domain control units (DCUs) will open new opportunities for semiconductor companies.

#### 16 Artificial-intelligence hardware: New opportunities for semiconductor companies

Artificial intelligence is opening the best opportunities for semiconductor companies in decades. How can they capture this value?

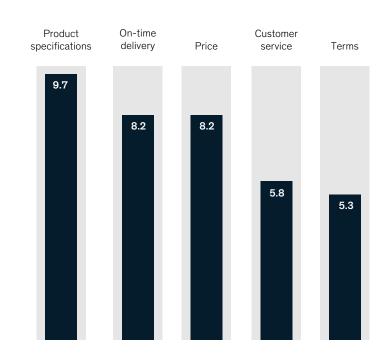

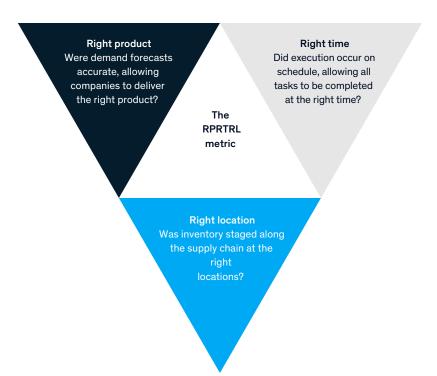

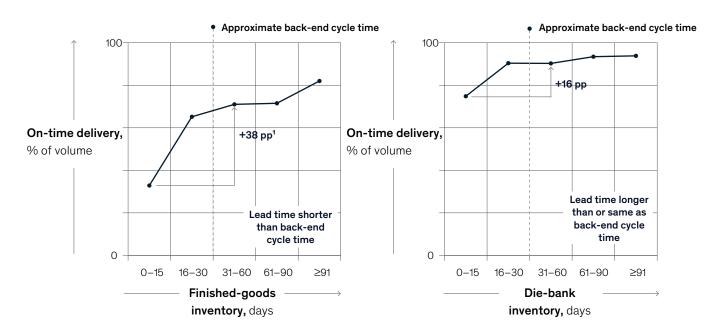

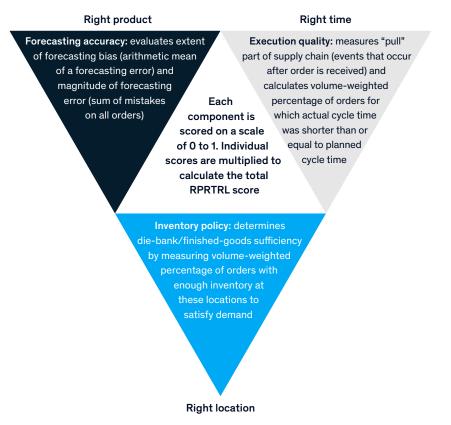

#### Right product, right time, right location: Quantifying the semiconductor supply chain

Problems along the semiconductor supply chain are difficult to diagnose. A new metric can help companies pinpoint performance issues.

27

#### Blockchain 2.0: What's in store for the two ends semiconductors (suppliers) and industrials (consumers)?

Ten years after blockchain's inception, it is presenting new opportunities for both suppliers, such as semiconductor companies, and consumers, such as industrials.

Digital tools could bring new productivity and efficiency gains to indirect functions. Why do semiconductor companies hesitate to use them?

63

50

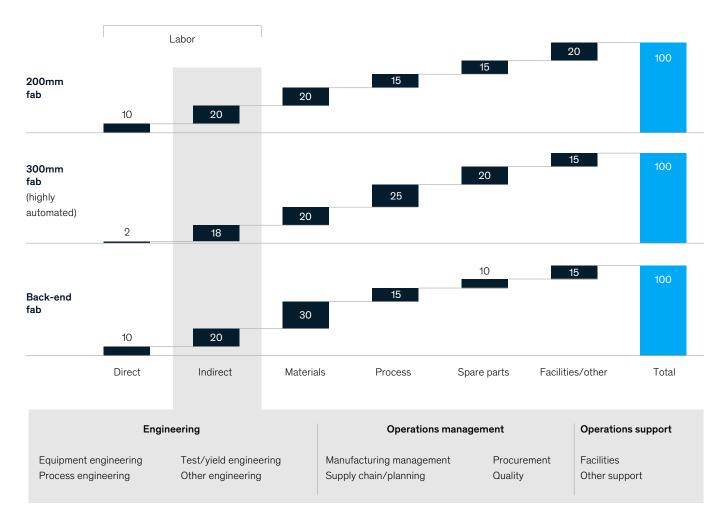

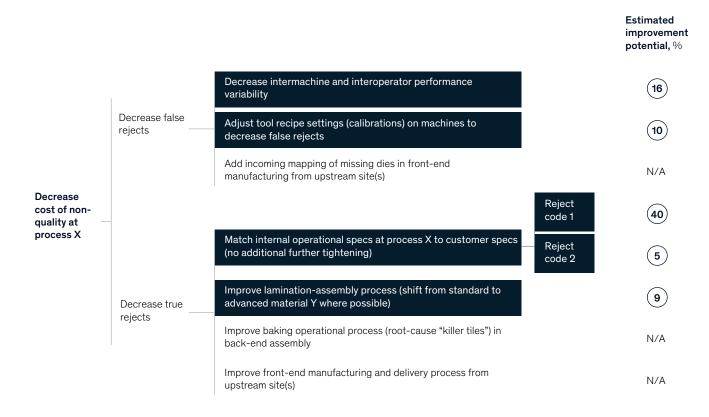

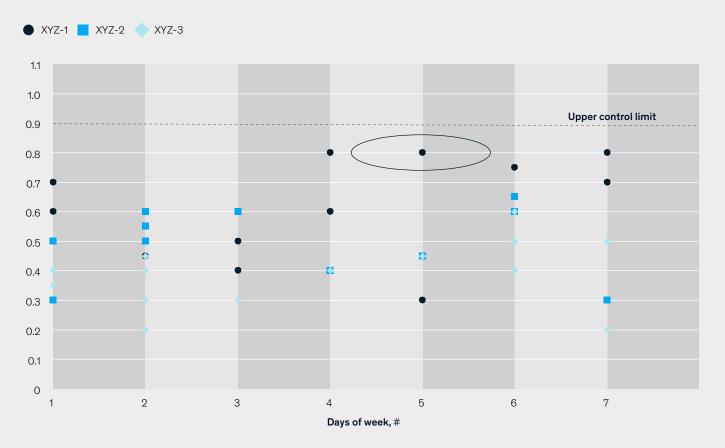

### Taking the next leap forward in semiconductor yield improvement

By prioritizing improvements in end-to-end yield, semiconductor companies can better manage cost pressures and sustain higher profitability. The path forward involves advanced analytics.

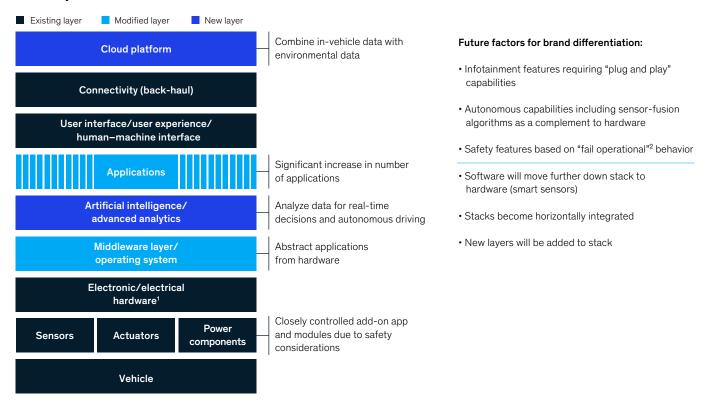

### **38** Rethinking car software and electronics architecture

As the car continues its transition from a hardware-driven machine to a software-driven electronics device, the auto industry's competitive rules are being rewritten.

## Introduction

Welcome to the seventh edition of McKinsey on Semiconductors. This publication appears at a time when our world is being transformed by the growth of artificial intelligence (AI), machine learning, and other innovative technologies. The pace of change is so fast that leading-edge products today may seem dated within a year. In this constantly evolving landscape, only one thing is certain: semiconductor companies will enable some of the most important technological leaps.

Many semiconductor companies are already benefiting from the innovative offerings, with the sector showing strong and rising profits over the past few years. But there may be challenges ahead, since companies that want to remain industry leaders must continue to increase their R&D investments. With costs in labor and other areas rising, some semiconductor companies may have difficulty finding additional funds for innovation. Moreover, some customers are already designing chips internally, and others may follow-a trend that could decrease sales. These concerns, and possible solutions, are the focus of the first article in this issue: "What's next for semiconductor profits and value creation?"

Other articles discuss recent technological trends that are increasing demand for chips. In "Artificialintelligence hardware: New opportunities for semiconductor companies," the authors explore how the rise of AI could help players capture more value. Overall, semiconductor growth from AI may be five times greater than growth from other sources. Opportunity is also the central theme of "Blockchain 2.0: What's in store for the two ends-semiconductors (suppliers) and industrials (consumers)?" As this article describes, blockchain's role in cryptocurrency and its potential growth as a business application may accelerate demand for chips. The extent of the change, as well as the timing, is still uncertain, but semiconductor leaders that monitor developments could have an advantage if blockchain takes off.

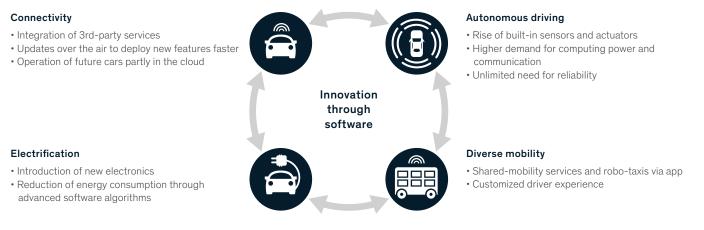

This issue also contains two articles that discuss a technology leap that has intrigued consumers: the rise of autonomous vehicles. "Rethinking car software and electronics architecture" explores how sensors and other automotive components may evolve, since these changes could influence chip demand. One specific shift-the rise of domain control units-is described in another article: "How will changes in the automotive-component market affect semiconductor companies?"

While all of these developments are exciting, semiconductor companies also have to deal with some stubborn problems that have plagued their businesses for years. Companies will discover a new approach to eliminating late shipments in "Right product, right time, right location: Quantifying the semiconductor supply chain." Similarly, they will learn about strategies for decreasing one of their largest costs in "Reducing indirect labor costs at semiconductor companies." The final article, "Taking the next leap forward in semiconductor yield improvement," will help companies use analytics and other strategies to optimize production in both line and die processes.

McKinsey on Semiconductors is designed to help industry executives navigate the road ahead and achieve continued growth. We hope that you find these articles helpful.

Ond S Koll

Ondrej Burkacky Partner

Peter Kenevan Senior partner

Abhijit Mahindroo Partner

## What's next for semiconductor profits and value creation?

Semiconductor profits have been strong over the past few years. Could recent changes within the industry stall their progress?

by Marc de Jong and Anurag Srivastava

© DuKai photographer/Getty Images

Outside Silicon Valley, the semiconductor industry's recent profitability seems unsurprising. The general assumption is that these players, like other tech companies, have long benefited from the rise of PCs, smartphones, and other devices. But insiders know that the industry's good fortune is a relatively recent phenomenon. While software players were achieving record gains for most of the past two decades, most semiconductor companies achieved limited economic profitability. Overall, only microprocessor companies and some fabless players could count on consistently strong returns, above the cost of capital.

Now the semiconductor sector is showing strong and rising profits. What's more, companies in virtually all subsegments are winning big. To discover how semiconductor companies engineered this turnaround, we analyzed trends related to economic profit (see sidebar, "Economic profit").<sup>1</sup> With this information, we wanted to answer an even more important question: What can semiconductor players do to ensure that the recent gains are not a blip but the emergence of a new industry norm?

#### A decade of change: How value creation has evolved within the semiconductor industry

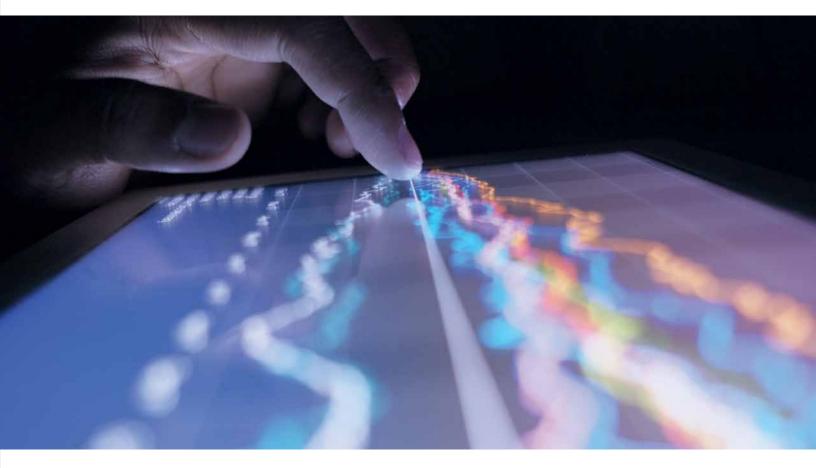

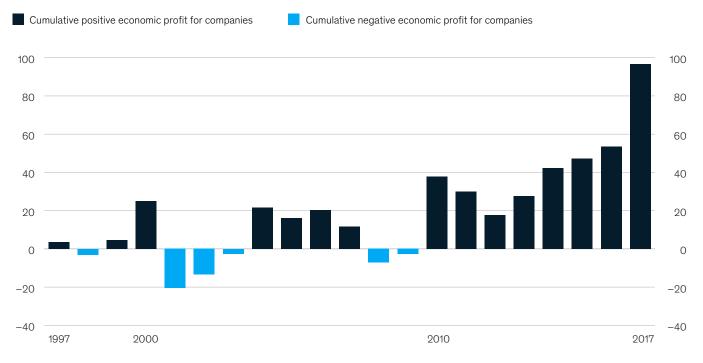

Only ten years ago, the semiconductor industry had mediocre returns. Although many companies were generating value, they lagged far behind their counterparts in other industries. But a much different story has unfolded over the past five years, with the semiconductor industry reporting record gains. In 2017 alone, it generated \$97 billion in economic profit—more than a threefold increase from the \$28 billion captured in 2013 (Exhibit 1).

<sup>1</sup> Economic profit equals the net operating profit after tax minus the capital charge (the invested capital, excluding goodwill—the amount of a purchase that exceeds the value of the assets involved) at previous year-end multiplied by the weighted average cost of capital.

#### Exhibit 1

#### From a value-creation perspective, 2017 was a record year for the semiconductor industry.

#### Economic-profit<sup>1</sup> value creation for semiconductor industry<sup>2</sup> (excluding goodwill), \$ billion

<sup>1</sup> Figures may not sum, because of rounding.

<sup>2</sup> About 273 companies across all industry subsegments.

Source: Annual reports; Semiconductor CPC database; McKinsey Corporate Performance Center

#### Economic profit

**When we looked** at value creation within the semiconductor industry, we deliberately restricted our analysis to economic profit, which is a periodic measure of value creation. In simplest terms, it is the amount left over after subtracting the cost of capital from net operating profit. The formula for computing it is as follows:

We chose to focus on economic profit because this metric comprehensively captures both profitability and the opportunity cost for the capital deployed. It also allowed us to perform reliable benchmark analyses for companies that followed many different business models. We only considered operating assets and excluded goodwill and other M&A intangibles. This approach allowed us to compare operating performance for different companies, regardless of whether their growth occurred organically or arose from a merger. For the years 2013 through 2017, however, we conducted two analyses: one factored in goodwill, and one did not (similar to the long-term analysis for 1997 through 2017). We conducted the two analyses to determine if the recent surge in M&A activity had a significant effect on results.

From 2012 to 2016, the semiconductor sector ranked tenth out of 59 major industries for value creation, placing it in the top 20 percent. That represents a big jump from the period from 2002 through 2006, when it ranked 18th.

#### Value creation has migrated to almost all subsegments.

Economic-profit value creation across subsegments (excluding goodwill), cumulative, \$ billion

#### Average annual economic profit (excluding goodwill), \$ billion

Source: Annual reports; Semiconductor CPC database; McKinsey Corporate Performance Center

From 2012 to 2016, the semiconductor sector ranked tenth out of 59 major industries for value creation, placing it in the top 20 percent. That represents a big jump from the period from 2002 through 2006, when it ranked 18th. While the semiconductor sector still lags far behind software, which was second only to biotechnology, it now outranks IT services, aerospace and defense, chemical, and many other major sectors for value creation.

Strong global economic growth since the 2008 recession has propelled the semiconductor industry's revenues, but an even more important factor involves the continued rise of the technology sector. Companies such as Alibaba, Amazon, Facebook, Google, and Tencent become more important to the global economy every year. These companies constantly introduce product or technology upgrades to remain competitive, and they need chips to enable such advances. Semiconductor companies have also benefited from increased digitization and cloud use across other industries, both of which accelerate chip demand.

In addition to these traditional revenue drivers, some recent technology innovations, including the Internet of Things, artificial-intelligence (AI) applications, and blockchain technology, have created new opportunities for semiconductor companies to capture value. Advances in the automotive industry, including vehicle electrification and the development of selfdriving cars, are also increasing chip demand. Such innovations are transforming how much value semiconductor companies capture from the technology stack. With AI applications, for instance, they could potentially achieve a larger share of total value than they did with PCs and mobile phones.

### Value trends within the semiconductor industry

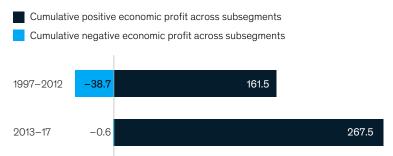

The rise in economic profit is not the only big shift within the semiconductor industry. As we reviewed the trends, we also found that value distribution has changed. From 1997 to 2012, the cumulative positive economic profit across segments was \$161.5 billion. But some segments also lost value (Exhibit 2).

Overall, value was highly concentrated in a few areas (Exhibit 3). The microprocessor subsegment generated the most value, followed by fabless. Together, they created almost all value in the industry, with all other subsegments roughly breaking even when their results were totaled.

#### From 1997 through 2012, the microprocessor and fabless subsegments created the most value.

#### Economic-profit<sup>1</sup> value creation by subsegment (excluding goodwill), 1997–2012 cumulative, \$ billion

Cumulative positive economic profit for companies

Top companies for economic profit, by subsegment

A) AMAT, ASML, KLA-Tencor; B) Synopsys, Cadence, Mentor graphics: C) ARM, Rambus, Spansion; D) Qualcomm, Mediatek, Xilinx; E) Intel; F) Samsung, Sandisk; G) Linear, Analog, Maxxim; H) TI, ON, NXP; I) Microchip, Powertech, Faraday; J) TSMC; K) Silicon-ware, Monolithic power.

<sup>1</sup> Figures may not sum, because of rounding.

<sup>2</sup> Intellectual property.

<sup>3</sup> Integrated device manufacturer.

Source: Annual reports; Semiconductor CPC database; McKinsey Corporate Performance Center

### From 1997 to 2012, the cumulative positive economic profit across segments was \$161.5 billion. But some segments also lost value.

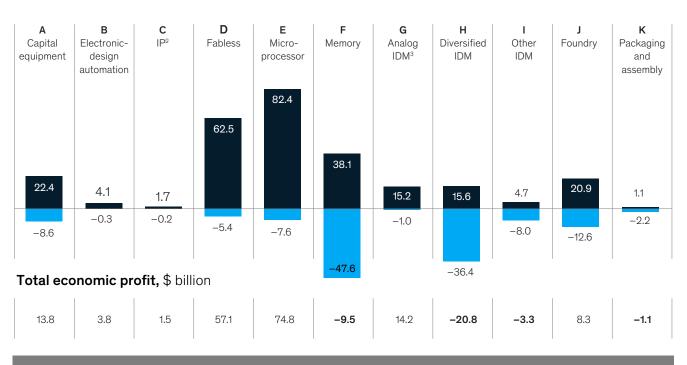

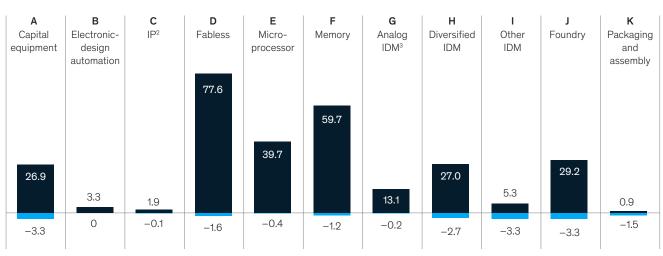

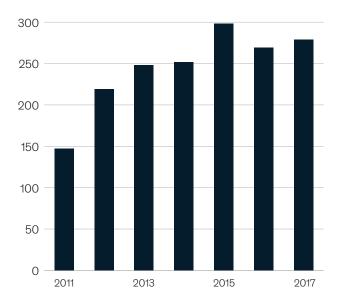

From 2013 to 2017, by contrast, nearly all subsegments recorded positive economic profit (Exhibit 4). Fabless was the best performer during this period, with memory in second place. The microprocessor subsegment came in third, down from the top ranking it held from 1997 to 2012. This shift occurred partly because PCs—key drivers of microprocessor demand—have seen much lower growth than smartphones and tablets, which often rely on chips designed by fabless players. Memory players have benefited from less oversupply, resulting in higher average sales prices and operating margins. Several factors may contribute to the greater distribution of value, including industry consolidation. First, many large conglomerates have divested their semiconductor units over the past ten years to reduce R&D investment and capital expenditures. Meanwhile, the industry has also undergone a wave of M&A across segments. The number of semiconductor companies fell from 208 in 2012 to 173 by 2017 (Exhibit 5). The fabless subsegment saw the most consolidation, followed by analog integrated device manufacturers and diversified integrated device manufacturers, but the drop in companies is notable in all sectors, including memory.

Exhibit 4

#### From 2013 through 2017, almost all subsegments demonstrated economic profit.

#### Economic-profit<sup>1</sup> value creation by subsegment (excluding goodwill), 2013-17 cumulative, \$ billion

Cumulative negative economic profit for companies

#### Total economic profit, \$ billion

| 23.6 | 3.3 | 1.8 | 76.0 | 39.3 | 58.4 | 12.9 | 24.3 | 2.0 | 25.9 | -0.6 |  |

|------|-----|-----|------|------|------|------|------|-----|------|------|--|

|      |     |     |      |      |      |      |      |     |      |      |  |

Top companies for economic profit, by subsegment

Cumulative positive economic profit for companies

A) AMAT, ASML, Lam Research; B) Synopsys, Cadence, Mentor graphics; C) ARM, Rambus, CEVA; D) Broadcomm, Qualcomm, Apple; E) Intel; F) Samsung, SK Hynix, Sandisk; G) Analog, Skyworks, Linear; H) TI, Toshiba, NXP; I) Microchip, Nuflare, Fingerprint; J) TSMC; K) ASE, Silicon-ware.

<sup>1</sup> Figures may not sum, because of rounding.

<sup>2</sup> Intellectual property.

<sup>3</sup> Integrated device manufacturer

Source: Annual reports; Semiconductor CPC database; McKinsey Corporate Performance Center

#### Industry consolidation over the past five years has likely contributed to improved profitability.

Companies with cumulative positive economic profit Companies with cumulative negative economic profit

#### Major deals or bankruptcies by subsegment

A) Mindspeed Tech: Acquired by MACOM, Mtekvision Assets: Became private, Transwitch Corp: Filed for bankruptcy; B) International Rectifier: Acquired by Infineon Tech, Supertex: Acquired by Microchip Technology; C) Altera Corp: Acquired by Intel, IBM Microelectronics: Acquired by GlobalFoundries, Spansion: Merged with Cypress; D) Actions Semiconductor: Became Private, Anadigics: Acquired by II-VI Inc., Fairchild Semicon: Acquired by ON; E) Applied Micro Circuits: Acquired by MACOM

Source: Annual reports; Semiconductor CPC database; McKinsey Corporate Performance Center

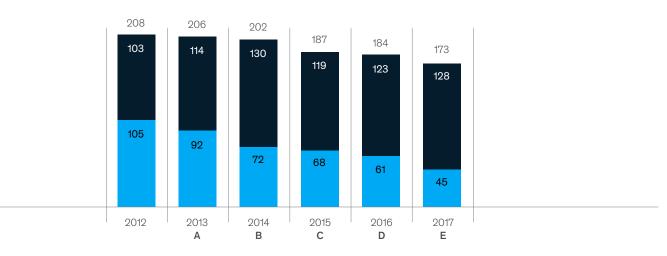

Because there's greater scale within subsegments, companies have more resources to invest in innovation and operating improvements. Their large size also helps them rebound when downturns occur in this highly cyclical industry, since they can take advantage of economies of scale and rely on more designs than in the past for their revenues. If one customer leaves, their bottom-line will not see the same hit as a smaller player with only a few accounts. Overall, down cycles have been milder and peaks have been higher within the semiconductor industry over the past few years (Exhibit 6).

Even when we factored goodwill—the amount of a purchase that exceeds the book value of the assets involved—into the calculation for the past five years, economic profit remained high. The fabless, memory, and microprocessor subsegments retained their

top three ranking. Results for value creation were similar across most other subsegments, although some notable declines occurred. For instance, in the microprocessor subsegment, the positive cumulative economic profit for the period from 2013 to 2017 would be reduced from \$39.7 billion to \$28.3 billion if goodwill is included. Since all semiconductor subsegments have engaged in M&A to a similar extent, it is not surprising that the relative rankings remained similar.

### Potential challenges: The rise of in-house chip design

After five successful years, semiconductor leaders across the industry have become a bit less optimistic about their prospects. Next to global tensions (hitting the semiconductor sector significantly, given the international value chains),

### Within the semiconductor industry, down cycles have been milder and peaks have been higher in past few years.

#### Economic-profit value creation by all subsegments (excluding goodwill), \$ billion

Source: Annual reports; Semiconductor CPC database; McKinsey Corporate Performance Center

one trend is generating new questions: the continued rise of in-house chip design at some of the semiconductor industry's largest customers.

This shift may be most prominent at Apple. While the company still relies on external providers for PC chips, it uses in-house designers to make the core chips for the iPhone, AppleTV, iWatch, and some other offerings. Apple then outsources chip manufacture to foundries. The company gains several advantages by taking this path:

Improved customer experience. Apple wants to optimize the customer experience and ensure that it is consistent across devices. While an external provider could create custom designs to meet these goals, an in-house team is more likely to satisfy the company's exacting specifications and possess the necessary technical knowledge.

- Competitive differentiation. By developing proprietary technology, Apple prevents other companies from replicating its customer experience.

- Insight into road maps. In-house creation gives Apple firsthand insight into processingtechnology capabilities, allowing it to create more accurate product road maps and enabling superior launch planning for new products. For each offering, it can specify how and when it must update other technology elements to complement the processor.

- Negotiating leverage. The sheer volume of chips designed in-house provides a strong negotiating position with foundries.

While Apple has conducted in-house work for many years, the scale, extent, and impact of these

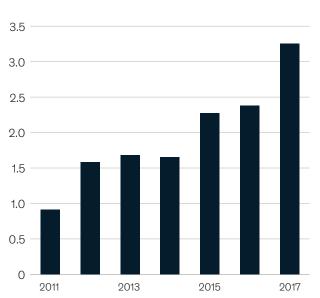

#### Apple has become a large fabless semiconductor company by designing its own chips.

Estimated economic value creation by Apple's semiconductor activities (excluding goodwill), 2011–17, \$ billion

Source: Alphr; Bloomberg; Business Insider; IHS Markit; S&P Capital IQ

operations might surprise even industry insiders (Exhibit 7). Apple is now the third largest fabless player in the world, behind Broadcom and Qualcomm Technologies. If the company were selling chips, its revenue would be around \$15 billion to \$20 billion annually, in line with Qualcomm Technology's. And based on current multiples, Apple's semiconductor business would be worth \$40 billion to \$80 billion.<sup>2</sup> These numbers speak volumes about the strength of Apple's internal chip operations.

Although shipments of iPhones and iPads appear to have peaked, Apple is still expected to expand its semiconductor footprint for iWatches and HomePods. It may also explore internal chip design for other products and components, such as those that enable power management and graphics.<sup>3</sup> If Apple does go down this path, an important source

Apple's total unit volume (iPhone, iPad, iPod, and iWatch), million

of revenue may further shift away from stand-alone semiconductor companies.

Many technology companies with deep pockets have taken notice of Apple's success with in-house chip design. Several, including large cloud players, are beginning to follow its example by developing AI chips.<sup>4</sup> They have already had some significant wins, such as Google's tensor-processing unit and Amazon's Graviton and Inferentia chips, all of which facilitate cloud computing.<sup>5</sup> In-house creation allows these companies to develop customized chips that offer better performance and security. Costs are also potentially lower, since companies do not have to pay a designer's premium. In the hotly competitive cloud market, these cost savings could help companies differentiate themselves from their rivals.

<sup>&</sup>lt;sup>2</sup> Based on a three- to fourfold revenue multiple of core Qualcomm Technology business (licensing business excluded).

<sup>&</sup>lt;sup>3</sup> Mark Gurman and Ian King, "Apple plans to use its own chips in Macs from 2020, replacing Intel," Bloomberg, April 2, 2018, bloomberg.com.

<sup>4</sup> Richard Waters, "Facebook joins Amazon and Google in Al chip race," *Financial Times*, February 18, 2019, ft.com; Argam Atashyan, "Amazon releases machine learning chips, namely Inferentia and Graviton," Gizchina Media, November 29, 2018, gizchina.com; Jordan Novet, "Microsoft is hiring engineers to work on A.I. chip design for its cloud," CNBC, June 11, 2018, cnbc.com.

<sup>&</sup>lt;sup>5</sup> Jordan Novet, "Microsoft is hiring engineers to work on A.I. chip design for its cloud," CNBC, June 11, 2018, cnbc.com; Tom Simonite, "New at Amazon: Its own chips for cloud computing," *Wired*, November 27, 2018, wired.com.

The development of ARM reference architectures, combined with the latest process improvements at state-of-the-art foundries, could now open the door to other tech companies that want to move design in-house—even those without deep pockets. If more companies begin designing chips in-house, the semiconductor industry will confront a new type of competitor—and that could have a long-term impact on demand and profitability.

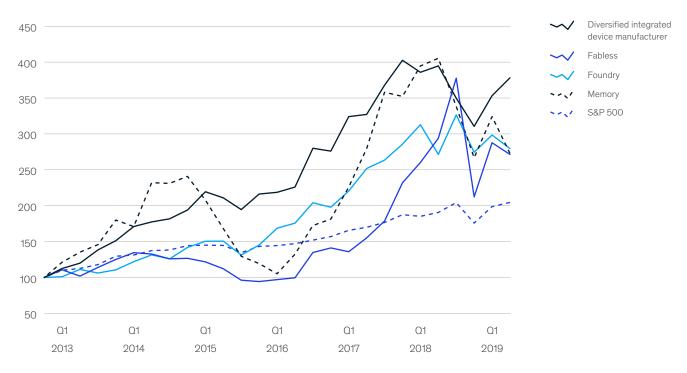

#### Looking ahead: Investor expectations

Economic profit is strongly correlated with total returns to shareholders (TRS) across industries. Overall, the semiconductor industry's TRS has declined about 10 percent since its peak in late 2018, partly because investors are worried that the weakening macroeconomic environment could affect semiconductor demand (Exhibit 8). A look at earnings multiples might suggest that investors are even less optimistic about the industry's long-term growth prospects. But it's more likely that they recognize that 2018 profitability for semiconductors was significantly higher when it reached the top of the cycle than it had been in past years. Even as profits inevitably trend downward, investors still expect them to reach historic levels.

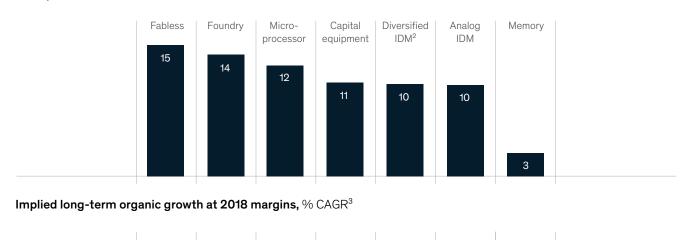

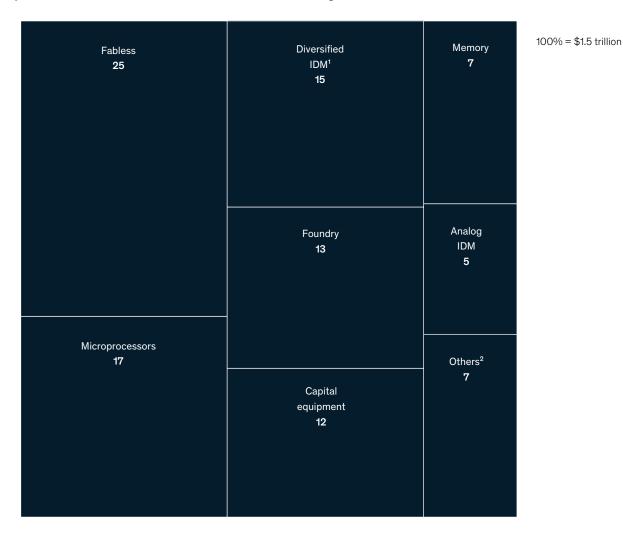

As for the subsegments, fabless now has the highest multiple, suggesting that investors think it will remain more profitable and might undergo additional M&A, which would increase its resilience (Exhibit 9). Memory, by contrast, has a low multiple, even though this subsegment has recently generated record profits. Investors may be concerned that this segment is more commoditized and therefore subject to sharper cyclic declines.

#### Exhibit 8

#### Total returns to shareholders have been strong within semiconductors.

Industry total returns to shareholders for the largest subsegments, index (Dec 31, 2012 = 100)

Source: Annual reports; S&P Capital IQ; Semiconductor CPC database

#### Performance expectations are highest for the fabless subsegment.

#### Enterprise value/EBITA<sup>1</sup> ratio, 2018

<sup>1</sup> Earnings before interest, taxes, and amortization; market data as of Dec 31, 2018.

<sup>2</sup> Integrated device manufacturer.

<sup>3</sup> Compound annual growth rate.

<sup>4</sup> Memory industry reached the peak of the valuation cycle in 2018 with extraordinarily high margins. Margin decline is imminent for the sector and is included in the sector valuation. At 2018 margins, valuation cannot be reconciled with topline decline alone.

Source: Annual reports; Semiconductor CPC database; McKinsey Corporate Performance Center

Fabless also has the highest enterprise value and is now the largest subsegment by far (Exhibit 10). Its ability to capture the highest economic profit, strong near-term growth prospects, and potential resiliency all contribute to higher investor expectations.

### Potential strategies for semiconductor companies

Given the current landscape, semiconductor companies must accelerate value creation. Four actions seem essential:

Creating strong road maps for leading customers. Semiconductor companies have long recognized the importance of delivering winning road maps for chip design, but the stakes are now higher than ever. In the past, customers that did not like a proposed road map might go to a competitor for their design needs. Such losses hurt, but they were often temporary because customers often came back to the original company for future designs. Now if customers are dissatisfied with a road map, they might move design capabilities in-house, resulting in a permanent loss of business.

N/A

Using M&A in moderation. The semiconductor industry is still fragmented in many subsegments, and industry consolidation still makes sense. The best strategy involves programmatic M&A, in which companies acquire at least one company a year, spending an average of 2 to 5 percent of their market capitalization, with no single deal accounting for more than 30 percent of their market capitalization.<sup>6</sup> These deals allow players

<sup>&</sup>lt;sup>6</sup> Chris Bradley, Martin Hirt, and Sven Smit, Strategy Beyond the Hockey Stick: People, Probabilities, and Big Moves to Beat the Odds, first edition, Hoboken, NJ: John Wiley & Sons, 2018.

#### Fabless captures the most shareholder value across subsegments.

Enterprise-value distribution across the semiconductor subsegments, % share

Note: Figures may not sum, because of rounding.

<sup>1</sup> Integrated device manufacturer.

<sup>2</sup> Includes intellectual property, electronic-design automation, packaging and assembly, and other IDM (discrete, opto, microcontroller unit). Source: S&P Capital IQ; McKinsey analysis

> to branch into adjacent areas to strengthen their competitive position. Deals that involve companies that only offer similar products will not produce as much value. One factor to consider when contemplating a deal is the value that it will bring to customers on measures such as price, quality, and performance. If an M&A

deal could improve any of these areas, it will help the companies create a more compelling road map that positions them for future success. But companies that undertake M&A must avoid falling into the trap of paying too much for goodwill, or else they risk destroying value.

- Maintaining price discipline across the cycle. The large companies that have emerged from deal making have the resources required to create leading-edge chips. But they will only win if they focus on smart capacity planning and maintain relatively stable prices across economic cycles, even if demand slows.

- Preparing for vertical integration among tech giants. Many large tech players may try to acquire small niche companies, especially if they have desirable intellectual property, so they can increase their semiconductor capabilities. Other large players may choose to license their technologies, rather than buying

chips, or to exit certain areas altogether instead of operating subscale.<sup>7</sup>

The semiconductor industry's recent move to value creation is impressive, but companies cannot assume that the strong profits will continue indefinitely. The move to in-house chip design among their most important customers could hit their bottom lines hard. While the pace and extent of this shift are still unknown, the best companies will begin preparing now by revamping their strategies.

<sup>7</sup> Benjamin Mayo, "Apple licenses Dialog power management tech, and hires 300 engineers, to develop more custom iPhone chips," 9to5Mac, October 10, 2018, 9to5mac.com.

Marc de Jong is a partner in McKinsey's Amsterdam office, and Anurag Srivastava is an alumnus of the New York office.

Copyright © 2019 McKinsey & Company. All rights reserved.

## Artificial-intelligence hardware: New opportunities for semiconductor companies

Artificial intelligence is opening the best opportunities for semiconductor companies in decades. How can they capture this value?

by Gaurav Batra, Zach Jacobson, Siddarth Madhav, Andrea Queirolo, and Nick Santhanam

© DuKai photographer/Getty Images

**Software has been the star of high tech** over the past few decades, and it's easy to understand why. With PCs and mobile phones, the game-changing innovations that defined this era, the architecture and software layers of the technology stack enabled several important advances. In this environment, semiconductor companies were in a difficult position. Although their innovations in chip design and fabrication enabled next-generation devices, they received only a small share of the value coming from the technology stack—about 20 to 30 percent with PCs and 10 to 20 percent with mobile.

But the story for semiconductor companies could be different with the growth of artificial intelligence (Al). Many Al applications have already gained a wide following, including virtual assistants that manage our homes and facial-recognition programs that track criminals. These diverse solutions, as well as other emerging Al applications, share one common feature: a reliance on hardware as a core enabler of innovation, especially for logic and memory functions.

What will this development mean for semiconductor sales and revenues? And which chips will be most important to future innovations? To answer these questions, we reviewed current AI solutions and the technology that enables them. We also examined opportunities for semiconductor companies across the entire technology stack. Our analysis revealed three important findings about value creation:

- Al could allow semiconductor companies to capture 40 to 50 percent of total value from the technology stack, representing the best opportunity they've had in decades.

- Storage will experience the highest growth, but semiconductor companies will capture the most value in compute, memory, and networking.

- To avoid mistakes that limited value capture in the past, semiconductor companies must undertake a new value-creation strategy that focuses on enabling customized, end-to-end solutions for specific industries, or "microverticals."

By keeping these beliefs in mind, semiconductor leaders can create a new road map for winning in Al.

This article begins by reviewing the opportunities that they will find across the technology stack, focusing on the impact of AI on hardware demand at data centers and the edge (computing that occurs with devices, such as self-driving cars). It then examines specific opportunities within compute, memory, storage, and networking. The article also discusses new strategies that can help semiconductor companies gain an advantage in the AI market, as well as issues they should consider as they plan their next steps.

#### The AI technology stack will open many opportunities for semiconductor companies

Al has made significant advances since its emergence in the 1950s, but some of the most important developments have occurred recently as developers created sophisticated machinelearning (ML) algorithms that can process large data sets, "learn" from experience, and improve over time. The greatest leaps came in the 2010s because of advances in deep learning (DL), a type of ML that can process a wider range of data, requires less data preprocessing by human operators, and often produces more accurate results.

To understand why AI is opening opportunities for semiconductor companies, consider the technology stack (Exhibit 1). It consists of nine discrete layers that allow the two activities that enable AI applications: training and inference (see sidebar "Training and inference"). When developers are trying to improve training and inference, they often encounter roadblocks related to the hardware layer, which includes storage, memory, logic, and networking. By providing next-generation accelerator architectures, semiconductor companies could increase computational efficiency or facilitate the transfer of large data sets through memory and storage. For instance, specialized memory for AI has 4.5 times more bandwidth than traditional memory, making it much better suited to handling the vast stores of big data that AI applications require. This performance improvement is so great that many customers would be more willing to pay the higher price that specialized memory requires (about \$25 per gigabyte, compared with \$8 for standard memory).

#### The technology stack for artificial intelligence (AI) contains nine layers.

| Technology                     | Stack             | Definition                                                                                                                                             | Memory                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Services Solution and use case |                   | Integrated solutions that include training data,<br>models, hardware, and other components (eg,<br>voice-recognition systems)                          | <ul> <li>Electronic data repository for<br/>short-term storage during<br/>processing</li> <li>Memory typically consists of DRAM<sup>1</sup></li> </ul>                                                                                                                                                                                                                          |  |  |

| Training Data types            |                   | Data presented to AI systems for analysis                                                                                                              | Storage                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Platform                       | Methods           | Techniques for optimizing weights given to model inputs                                                                                                | <ul> <li>Electronic repository for long-term<br/>storage of large data sets</li> </ul>                                                                                                                                                                                                                                                                                          |  |  |

|                                | Architecture      | Structured approach to extract features from data (eg, convolutional or recurrent neural networks)                                                     | Storage typically consists of NAND <sup>2</sup>                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                | Algorithm         | A set of rules that gradually modifies the weights given to<br>certain model inputs within the neural network during<br>training to optimize inference | <ul> <li>Logic</li> <li>Processor optimized to calculate<br/>neural-network operations, ie,<br/>convolution and matrix multiplication</li> <li>Logic devices are typically CPU,<br/>GPU, FPGA, and/or ASIC<sup>3</sup></li> <li>Networking</li> <li>Switches, routers, and other<br/>equipment used to link servers<br/>in the cloud and to connect<br/>edge devices</li> </ul> |  |  |

|                                | Framework         | Software packages to define architectures and invoke algorithms on the hardware through the interface                                                  |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Interface                      | Interface systems | Systems within framework that determine and facilitate communication pathways between software and underlying hardware                                 |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Hardware                       | Head node         | Hardware unit that orchestrates and coordinates computations among accelerators                                                                        |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                | Accelerator       | Silicon chip designed to perform highly parallel operations                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                |                   | required by AI; also enables simultaneous computations                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

<sup>1</sup> Dynamic random access memory.

<sup>2</sup> Not AND.

<sup>3</sup> CPU = central processing unit, GPU = graphics-processing unit, FPGA = field programmable gate array, ASIC = application-specific integrated circuit. Source: Expert interviews; literature search

#### AI will drive a large portion of semiconductor revenues for data centers and the edge

With hardware serving as a differentiator in AI, semiconductor companies will find greater demand for their existing chips, but they could also profit by developing novel technologies, such as workloadspecific AI accelerators (Exhibit 2). We created a model to estimate how these AI opportunities would affect revenues and to determine whether AI-related chips would constitute a significant portion of future demand (see sidebar "How we estimated value" for more information on our methodology).

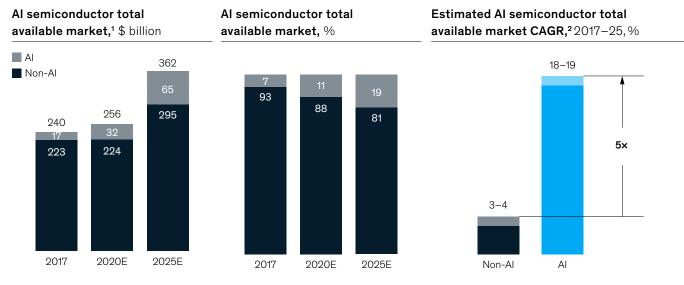

Our research revealed that AI-related semiconductors will see growth of about 18 percent annually over the next few years—five times greater than the rate for semiconductors used in non-AI applications (Exhibit 3). By 2025, AI-related semiconductors could account for almost 20 percent of all demand, which would translate into about \$65 billion in revenue. Opportunities will emerge at both data centers and the edge. If this growth materializes as expected, semiconductor companies will be positioned to capture more value from the AI technology stack than they have obtained with previous innovations—about 40 to 50 percent of the total.

#### AI will drive most growth in storage, but the best opportunities for value creation lie in other segments

We then took our analysis a bit further by looking at specific opportunities for semiconductor players within compute, memory, storage, and networking.

### Companies will find many opportunities in the artificial intelligence (AI) market, with leaders already emerging.

|            | Opportunities in existing market                                                                             | Potential new opportunities                                                                |  |  |

|------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Compute    | <ul> <li>Accelerators for parallel processing, such as GPUs<sup>1</sup><br/>and FPGAs<sup>2</sup></li> </ul> | Workload-specific AI accelerators                                                          |  |  |

| Memory     | <ul> <li>High-bandwidth memory</li> <li>On-chip memory (SRAM<sup>3</sup>)</li> </ul>                         | • NVM <sup>4</sup> (as memory device)                                                      |  |  |

| Storage    | Potential growth in demand for existing storage systems     as more data are retained                        | <ul> <li>Al-optimized storage systems</li> <li>Emerging NVM (as storage device)</li> </ul> |  |  |

| Networking | Infrastructure for data centers                                                                              | <ul><li>Programmable switches</li><li>High-speed interconnect</li></ul>                    |  |  |

Graphics-processing units.

<sup>2</sup> Field programmable gate arrays.

<sup>3</sup> Static random access memory.

<sup>4</sup> Nonvolatile memory.

Source: McKinsey analysis

For each area, we examined how hardware demand is evolving at both data centers and the edge. We also quantified the growth expected in each category except networking, where AI-related opportunities for value capture will be relatively small for semiconductor companies.

#### Compute

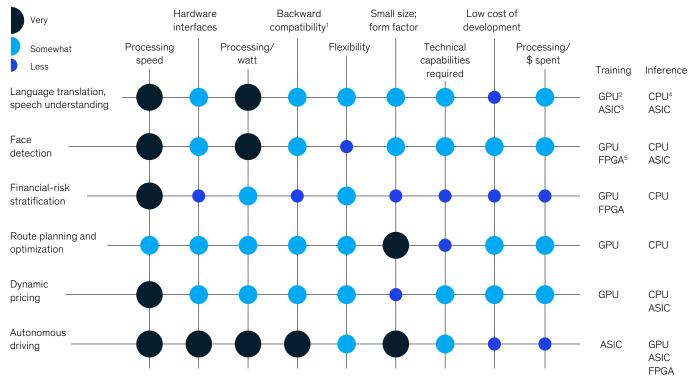

Compute performance relies on central processing units (CPUs) and accelerators—graphicsprocessing units (GPUs), field programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs). Since each use case has different compute requirements, the optimal AI hardware architecture will vary. For instance, route-planning applications have different needs for processing speed, hardware interfaces, and other performance features than applications for autonomous driving or financial-risk stratification (Exhibit 4).

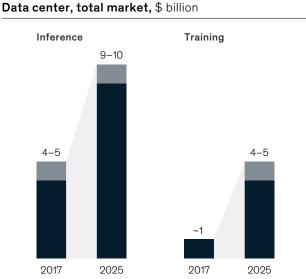

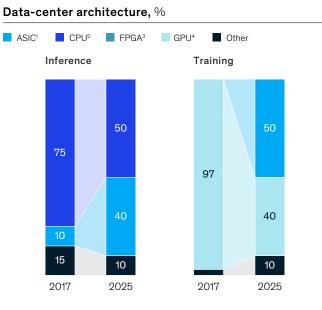

Overall, demand for compute hardware will increase through 2025 (Exhibit 5). After analyzing more than 150 DL use cases, looking at both inference and training requirements, we were able to identify the architectures most likely to gain ground in data centers and the edge (Exhibit 6). Data-center usage. Most compute growth will stem from higher demand for AI applications at cloudcomputing data centers. At these locations, GPUs are now used for almost all training applications. We expect that they will soon begin to lose market share to ASICs, until the compute market is about evenly divided between these solutions by 2025. As ASICs enter the market, GPUs will likely become more customized to meet the demands of DL. In addition to ASICs and GPUs, FPGAs will have a small role in future AI training, mostly for specialized data-center applications that must reach the market quickly or require customization, such as those for prototyping new DL applications.

For inference, CPUs now account for about 75 percent of the market. They'll lose ground to ASICs as DL applications gain traction. Again, we expect to see an almost equal divide in the compute market, with CPUs accounting for 50 percent of demand in 2025 and ASICs for 40 percent.

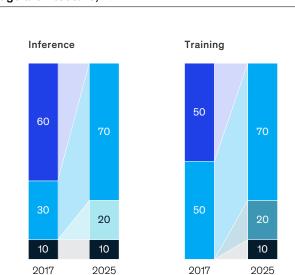

*Edge applications.* Most edge training now occurs on laptops and other personal computers, but more devices may begin recording data and playing a role in on-site training. For instance, drills used during oil and gas exploration generate data related to a well's geological characteristics that could be used to train models. For accelerators, the training market is now evenly divided between CPUs and ASICs. In the future, however, we expect that ASICs built into systems on chips will account for 70 percent of demand. FPGAs will represent about 20 percent of demand and will be used for applications that require significant customization.

When it comes to inference, most edge devices now rely on CPUs or ASICs, with a few applications—such as autonomous cars—requiring GPUs. By 2025, we expect that ASICs will account for about 70 percent of the edge inference market and GPUs 20 percent.

#### Memory

Al applications have high memory-bandwidth requirements, since computing layers within deep neural networks must pass input data to thousands of cores as quickly as possible. Memory is required—typically dynamic random access memory (DRAM)-to store input data, weigh model parameters, and perform other functions during both inference and training. Consider a model being trained to recognize the image of a cat. All intermediate results in the recognition processfor example, colors, contours, and textures-need to reside on memory as the model fine-tunes its algorithms. Given these requirements, AI will create a strong opportunity for the memory market, with value expected to increase from \$6.4 billion in 2017 to \$12.0 billion in 2025. That said, memory will see the lowest annual growth of the three accelerator categories-about 5 to 10 percent-because of efficiencies in algorithm design, such as reduced bit precision, as well as capacity constraints in the industry relaxing.

Most short-term memory growth will result from increased demand at data centers for the highbandwidth DRAM required to run Al, ML, and

#### Training and inference

#### All artificial-intelligence (AI)

applications must be capable of training and inference. To understand the importance of these tasks, consider their role in helping self-driving cars avoid obstacles. During the training phase, developers present images to the neural network—for instance, those of dogs or pedestrians—and perform recognition tests. They then refine network parameters until the neural network displays high accuracy in visual detection. After the network has viewed millions of images and is fully trained, it enables recognition of dogs and pedestrians during the inference phase. The cloud is an ideal location for training because it provides access to vast stores of data from multiple servers—and the more information an AI application reviews during training, the better its algorithm will become. Further, the cloud can reduce expenses because it allows graphics-processing units (GPUs) and other expensive hardware to train multiple AI models. Since training occurs intermittently on each model, capacity is not an issue.

With inference, AI algorithms handle less data but must generate responses more rapidly. A self-driving car doesn't have time to send images to the cloud for processing once it detects an object in the road, nor do medical applications that evaluate critically ill patients have leeway when interpreting brain scans after a hemorrhage. And that makes the edge, or in-device computing, the best choice for inference.

### Growth for semiconductors related to artificial intelligence (AI) is expected to be five times greater than growth in the remainder of the market.

<sup>1</sup> Total available market includes processors, memory, and storage; excludes discretes, optical, and micro-electrical-mechanical systems. <sup>2</sup> Compound annual growth rate.

Source: Bernstein; Cisco Systems; Gartner; IC Insights; IHS Markit; Machina Research; McKinsey analysis

DL algorithms. But over time, the demand for Al memory at the edge will increase—for instance, connected cars may need more DRAM.

Current memory is typically optimized for CPUs, but developers are now exploring new architectures. Solutions that are attracting more interest include the following:

High-bandwidth memory (HBM). This technology allows AI applications to process large data sets at maximum speed while minimizing power requirements. It allows DL compute processors to access a three-dimensional stack of memory through a fast connection called through-silicon via (TSV). AI chip leaders such as Google and Nvidia have adopted HBM as the preferred memory solution, although it costs three times more than traditional DRAM per gigabyte—a move

that signals their customers are willing to pay for expensive AI hardware in return for performance gains.<sup>1</sup>

On-chip memory. For a DL compute processor, storing and accessing data in DRAM or other outside memory sources can take 100 times more time than memory on the same chip. When Google designed the tensor-processing unit (TPU), an ASIC specialized for AI, it included enough memory to store an entire model on the chip.<sup>2</sup> Start-ups such as Graphcore are also increasing on-chip memory capacity, taking it to a level about 1,000 times more than what is found on a typical GPU, through a novel architecture that maximizes the speed of AI calculations. The cost of on-chip memory is still prohibitive for most applications, and chip designers must address this challenge.

<sup>&</sup>lt;sup>1</sup> Liam Tung, "GPU killer: Google reveals just how powerful its TPU2 chip really is," ZDNet, December 14, 2017, zdnet.com.

<sup>&</sup>lt;sup>2</sup> Kaz Sato, "What makes TPUs fine-tuned for deep learning?," Google, August 30, 2018, google.com.

#### The optimal compute architecture will vary by use case.

#### Example use-case analysis of importance

<sup>1</sup> Can use interfaces and data from earlier versions of the system.

<sup>2</sup> Graphics-processing unit.

<sup>3</sup> Application-specific integrated circuit.

<sup>4</sup> Central processing unit.

<sup>5</sup> Field programmable gate array.

Source: McKinsey analysis

#### Storage

Al applications generate vast volumes of data—about 80 exabytes per year, which is expected to increase to 845 exabytes by 2025. In addition, developers are now using more data in Al and DL training, which also increases storage requirements. These shifts could lead to annual growth of 25 to 30 percent from 2017 to 2025 for storage—the highest rate of all segments we examined.<sup>3</sup> Manufacturers will increase their output of storage accelerators in response, with pricing dependent on supply staying in sync with demand.

Unlike traditional storage solutions that tend to take a one-size-fits-all approach across different use cases, AI solutions must adapt to changing needsand those depend on whether an application is used for training or inference. For instance, AI training systems must store massive volumes of data as they refine their algorithms, but AI inference systems only store input data that might be useful in future training. Overall, demand for storage will be higher for AI training than inference.

One potential disruption in storage is new forms of nonvolatile memory (NVM). New forms of NVM have characteristics that fall between traditional memory, such as DRAM, and traditional storage, such as NAND flash. They can promise higher density than DRAM, better performance than NAND, and better power consumption than both. These characteristics will enable new applications

<sup>&</sup>lt;sup>3</sup> When exploring opportunities for semiconductor players in storage, we focused on not AND (NAND). Although demand for hard-disk drives will also increase, this growth is not driven by semiconductor advances.

#### At both data centers and the edge, demand for training and inference hardware is growing.

### Inference Training 4 - 4.51 - 1.5<0.1 < 0.1 2017 2025 2017 2025

Source: Expert interviews; McKinsey analysis

and allow NVM to substitute for DRAM and NAND in others. The market for these forms of NVM is currently small-representing about \$1 billion to \$2 billion in revenue over the next two years-but it is projected to account for more than \$10 billion in revenue by 2025.

The NVM category includes multiple technologies, all of which differ in memory access time and cost and are all in various stages. Magnetoresistive random-access memory (MRAM) has the lowest latency for read and write, with greater than fiveyear data retention and excellent endurance. However, its capacity scaling is limited, making it a costly alternative that may be used for frequently accessed caches rather than a long-term dataretention solution. Resistive random-access memory (ReRAM) could potentially scale vertically, giving it an advantage in scaling and cost, but it has slower latency and reduced endurance. Phasechange memory (PCM) fits in between the two, with 3D XPoint being the most well-known example. Endurance and error rate will be key barriers that must be overcome before more widespread adoption.

#### Networking

Edge, total market, \$ billion

Al applications require many servers during training, and the number increases with time. For instance, developers only need one server to build an initial Al model and under 100 to improve its structure. But training with real data-the logical next stepcould require several hundred. Autonomous-driving models require more than 140 servers to reach 97 percent accuracy in detecting obstacles.

If the speed of the network connecting servers is slow-as is usually the case-it will cause training bottlenecks. Although most strategies for improving network speed now involve datacenter hardware, developers are investigating other options, including programmable switches that can route data in different directions. This capability will accelerate one of the most important training tasks: the need to resynchronize input weights among multiple servers whenever model parameters are updated. With programmable switches, resynchronization can occur almost instantly, which could increase training speed from two to ten times. The greatest performance gains would come with large AI models, which use the most servers.

Another option to improve networking involves using high-speed interconnections in servers. This technology can produce a threefold improvement in performance, but it's also about 35 percent more expensive.

### Semiconductor companies need new strategies for the AI market

It's clear that opportunities abound, but success isn't guaranteed for semiconductor players. To capture the value they deserve, they'll need to focus on end-to-end solutions for specific industries (also called microvertical solutions), ecosystem development, and innovation that goes far beyond improving compute, memory, and networking technologies.

#### Customers will value end-to-end solutions for microverticals that deliver a strong return on investment

Al hardware solutions are only useful if they're compatible with all other layers of the technology stack, including the solutions and use cases in the services layer. Semiconductor companies can take two paths to achieve this goal, and a few have already begun doing so. First, they could work with partners to develop Al hardware for industry-specific use cases, such as oil and gas exploration, to create an end-to-end solution. For example, Mythic has developed an ASIC to support edge inference for image- and voice-recognition applications within the healthcare and military industries. Alternatively, semiconductor companies could focus on developing Al hardware that enables broad, cross-industry solutions, as Nvidia does with GPUs.

The path taken will vary by segment. With memory and storage players, solutions tend to have the same technology requirements across microverticals. In compute, by contrast, AI algorithm requirements may vary significantly. An edge accelerator in an autonomous car must process much different data from a language-translation application that relies on the cloud. Under these circumstances, companies cannot rely on other players to build other layers of the stack that will be compatible with their hardware.

### Active participation in ecosystems is vital for success

Semiconductor players will need to create an ecosystem of software developers that prefer their hardware by offering products with wide appeal. In return, they'll have more influence over design choices. For instance, developers who prefer a certain hardware will use that as a starting point when building their applications. They'll then look for other components that are compatible with it.

To help draw software developers into their ecosystem, semiconductor companies should reduce complexity whenever possible. Since

#### How we estimated value

#### We took a bottom-up approach

to estimate the value at stake for semiconductor companies. Consider accelerators used for compute functions. First, we determined the percent of servers in data centers that were used for artificial intelligence (Al). We then identified the type of logic device they commonly used and the average sales price for related accelerators. For edge computing, we conducted a similar review, but we focused on determining the number of devices that were used for AI, rather than servers. By combining our insights for data centers and edge devices, we could estimate the potential value for semiconductor companies related to compute functions.

#### The preferred architectures for compute are shifting in data centers and the edge.

Edge architecture, %

<sup>1</sup> Application-specific integrated circuit.

<sup>2</sup> Central processing unit.

<sup>3</sup> Field programmable gate array.

<sup>4</sup> Graphics-processing unit.

Source: Expert interviews; McKinsey analysis

there are now more types of AI hardware than ever, including new accelerators, players should offer simple interfaces and software-platform capabilities. For instance, Nvidia provides developers with Compute Unified Device Architecture, a parallel-computing platform and application programming interface (API) that works with multiple programming languages. It allows software developers to use Compute Unified Device Architecture–enabled GPUs for generalpurpose processing. Nvidia also provides software developers with access to a collection of primitives for use in DL applications. The platform has now been deployed across thousands of applications.

Within strategically important industry sectors, Nvidia also offers customized software-development kits. To assist with the development of software for selfdriving cars, for instance, Nvidia created DriveWorks, a kit with ready-to-use software tools, including object-detection libraries that can help applications interpret data from cameras and sensors in selfdriving cars.

As preference for certain hardware architectures builds throughout the developer community, semiconductor companies will see their visibility soar, resulting in better brand recognition. They'll also see higher adoption rates and greater customer loyalty, resulting in lasting value.

Only platforms that add real value to end users will be able to compete against comprehensive offerings from large high-tech players, such as Google's TensorFlow, an open-source library of ML and DL models and algorithms.<sup>4</sup> TensorFlow supports Google's core products, such as Google Translate, and also helps the company solidify its position within the AI technology stack, since TensorFlow is compatible with multiple compute accelerators.

<sup>4</sup> An open-source, machine-learning framework for everyone, available at tensorflow.org.

### Innovation is paramount, and players must go up the stack

Many hardware companies that want to enable AI innovation focus on improving the computation process. Traditionally, this strategy has involved offering optimized compute accelerators or streamlining paths between compute and data through innovations in memory, storage, and networking. But hardware companies should go beyond these steps and seek other forms of innovation by going up the stack. For example, Al-based facial-recognition systems for secure authentication on smartphones were enabled by specialized software and a 3-D sensor that projects thousands of invisible dots to capture a geometric map of a user's face. Because these dots are much easier to process than several millions of pixels from cameras, these authentication systems work in a fraction of a second and don't interfere with the user experience. Hardware companies could also think about how sensors or other innovative technologies can enable emerging Al use cases.

### Semiconductor companies must define their AI strategy now

Semiconductor companies that take the lead in AI will be more likely to attract and retain customers and ecosystem partners—and that could prevent later entrants from attaining a leading position in the market. With both major technology players and start-ups launching independent efforts in the AI hardware space now, the window of opportunity for staking a claim will rapidly shrink over the next few years. To establish a strong strategy now, they should focus on three questions:

Where to play? The first step to creating a focused strategy involves identifying the target industry microverticals and AI use cases. At the most basic level, this involves estimating the size of the opportunity within different verticals, as well as the particular pain points that AI solutions could eliminate. On the technical side, companies should decide if they want to focus on hardware for data centers or the edge.

- How to play? When bringing a new solution to market, semiconductor companies should adopt a partnership mind-set, since they might gain a competitive edge by collaborating with established companies within specific industries. They should also determine what organizational structure will work best for their business. In some cases, they might want to create groups that focus on certain functions, such as R&D, for all industries. Alternatively, they could dedicate groups to select microverticals, allowing them to develop specialized expertise.

- When to play? Many companies might be tempted to jump into the AI market, since the cost of being a follower is high, particularly with DL applications. Further, barriers to entry will rise as industries adopt specific AI standards and expect all players to adhere to them. While rapid entry might be the best approach for some companies, others might want to take a more measured approach that involves slowly increasing their investment in select microverticals over time.

The AI and DL revolution gives the semiconductor industry the greatest opportunity to generate value that it has had in decades. Hardware can be the differentiator that determines whether leading-edge applications reach the market and grab attention. As AI advances, hardware requirements will shift for compute, memory, storage, and networking—and that will translate into different demand patterns. The best semiconductor companies will understand these trends and pursue innovations that help take AI hardware to a new level. In addition to benefiting their bottom line, they'll also be a driving force behind the AI applications transforming our world.

**Gaurav Batra** is a partner in McKinsey's Washington, DC, office; **Zach Jacobson** and **Andrea Queirolo** are associate partners in the New York office; **Siddarth Madhav** is a partner in the Chicago office; and **Nick Santhanam** is a senior partner in the Silicon Valley office.

The authors wish to thank Sanchi Gupte, Jo Kakarwada, Teddy Lee, and Ben Byungchol Yoon for their contributions to this article.

Copyright © 2019 McKinsey & Company. All rights reserved.

## Blockchain 2.0: What's in store for the two ends semiconductors (suppliers) and industrials (consumers)?

Ten years after blockchain's inception, it is presenting new opportunities for both suppliers, such as semiconductor companies, and consumers, such as industrials.

by Gaurav Batra, Rémy Olson, Shilpi Pathak, Nick Santhanam, and Harish Soundararajan

© Imaginima/Getty Images

Blockchain is best known as a sophisticated and somewhat mysterious technology that allows cryptocurrencies to change hands online without assistance from banks or other intermediaries. But in recent years, it has also been promoted as the solution to business issues ranging from fraud management to supply-chain monitoring to identity verification. Despite the hype, however, blockchain's use in business is still largely theoretical. A few pioneers in retail and other sectors are exploring blockchain business applications related to supplychain management and other processes, but most are reluctant to proceed further because of high costs, unclear returns, and technical difficulties.

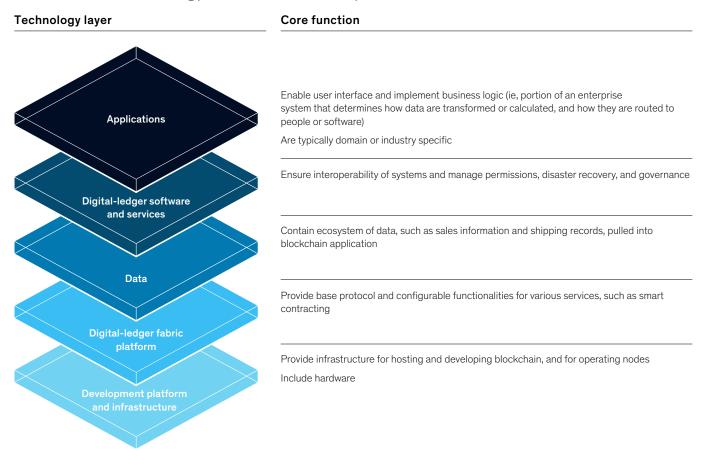

But we may now be at a transition point between Blockchain 1.0 and Blockchain 2.0. In the new era, blockchain-enabled cryptocurrency applications will likely cede their prominence to blockchain business applications that can potentially increase efficiency and reduce costs. These applications will be in a good position to gain steam, since many large tech companies may soon begin offering blockchain as a service (BaaS). Rather than just providing the hardware layer, as they've traditionally done, these companies will extend their services up the technology stack to blockchain platforms and tools. As blockchain deployment becomes less complex and expensive, companies that have sat on the sidelines may now be willing to take the plunge. (See sidebar, "What advantages do blockchain business applications offer?")

Will blockchain business applications continue to grow and finally validate their promise? Industrial companies, which were largely on the sidelines during the Blockchain 1.0 era, want an answer to this question because they could find opportunities to deploy business applications that improve their bottom line. Semiconductor companies are also interested in the growth of both blockchain business applications and blockchain-enabled cryptocurrency because this could increase demand for chips.

Both industrial and semiconductor players will need a solid understanding of specific blockchainenabled use cases and the market landscape to succeed in the new era. To assist them, this article reviews the changing market and then focuses on specific strategies for capturing value. One caveat: all information in this article reflects data available as of December 2018. Cryptocurrency values fluctuate widely, so the numbers reported, including those for market capitalization, may not reflect the most recent data. Blockchain technology and the competitive landscape are also evolving rapidly, and there may have been changes since publication.

#### Blockchain 1.0: The cryptocurrency era

It is not surprising that many people conflate blockchain with Bitcoin, the first and most dominant cryptocurrency. Until recently, the vast majority of blockchain applications involved enabling cryptocurrency transactions. Around 2014, however, private companies began investigating the use of blockchain for other business applications. Since most of these players are still at the pilot stage, it is fair to say that blockchain-enabled cryptocurrency has been the focus of the Blockchain 1.0 era.

#### The emergence of cryptocurrencies

Bitcoin hit the market in 2009 as an open-source software application. It was first used in a commercial transaction in 2010, when two pizzas were bought for 10,000 bitcoin (under \$10 then, but about \$35 million as of December 2018). With no central authority or server to verify transactions, the public was initially skeptical about Bitcoin and reluctant to use it. Beginning in 2014, however, Bitcoin experienced a meteoric increase in user base, brand-name recognition, and transaction volume. Its value is extremely volatile, however, and it has declined sharply from its late 2017 peak of more than \$19,000.

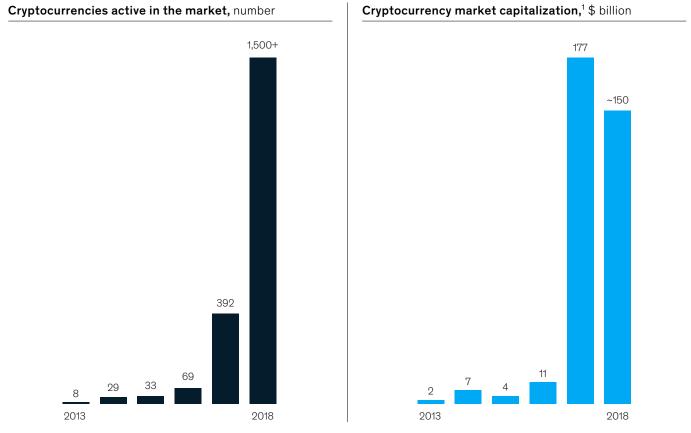

The past two years have seen the most growth in blockchain-enabled cryptocurrencies, with the number increasing from 69 in 2016 to more than 1,500 in 2018. Even though Bitcoin's value has decreased this year, an influx of initial coin offerings (ICOs) has increased the market capitalization for cryptocurrencies (Exhibit 1).

Many of the additional currencies—also called "altcoins"—were created to address certain gaps or inefficiencies with Bitcoin, and they are available through various networks. Popular altcoins include Dash, Litecoin, and XRP (offered through Ripple). Of all the alternative cryptocurrency networks, Ethereum is most popular. It is an open-source platform that allows users to build and launch decentralized applications, including cryptocurrencies or digital ledgers. Users must spend a specific digital currency, Ether, to run applications on Ethereum. Ether can also serve as an alternative to regular money, but its primary purpose is to facilitate Ethereum operations.

Together, the market capitalization of a select set of major cryptocurrencies was about \$150 billion in December 2018, with Bitcoin and the four leading altcoins representing about 75 percent of this value. Bitcoin's market capitalization of about \$60 billion was the highest.

#### **Transaction verification**

The method used to verify transactions varies by cryptocurrency. With Bitcoin, the first participant, or "miner," to validate a transaction and add a new block of data to the digital ledger will receive a certain number of tokens as a reward. Under this model, which is referred to as a proof-of-work (PoW) system, miners have an incentive to act quickly. But validating a transaction doesn't simply involve verifying that Bitcoin has been transferred from one account to another. Instead, a miner has to answer a cryptographic question by correctly identifying an alphanumeric series associated with the transaction. This activity requires a lot of trial and error, making the hash rate-the compute speed at which an operation is completedextremely important with Bitcoin.

Exhibit1

#### The number of active cryptocurrencies and their market capitalization has soared.

<sup>1</sup> This is the market capitalization for a select bundle of cryptocurrencies. Bundle includes: Bitcoin, Dash, Ethereum, Litecoin, Ripple, and several other altcoins. Figures are as of Dec 11, 2018.

In the beginning, many individuals mined Bitcoin as a hobby. But as interest in cryptocurrencies grew, the number and size of Bitcoin miners soared, necessitating more sophisticated hardware and more intense computing power. This shift has favored the rise of large mining pools. Many of these, including AntPool and BTC.COM, are based in China. The top five mining pools account for 70 to 85 percent of the overall Bitcoin network's collective hash rate, or computing power.

#### Hardware for cryptocurrency players

In the early day of cryptocurrency, amateur hobbyists relied on central processing units (CPUs) to optimize compute performance. When the Bitcoin network began expanding around 2010, the graphics-processing unit (GPU) replaced the CPU as the accelerator of choice. The ascent of GPUs was short lived, however, since many companies began designing application-specific integrated circuits (ASICs) for cryptocurrency mining to improve hash rates.

About 50 to 60 percent of companies that manufacture ASICs for Bitcoin transactions are based in the Greater China region (Exhibit 2). (Some of these began creating ASICs for cryptocurrency mining before Bitcoin entered the market in 2008, since this was already viewed as a potential growth area.) BitMain Technologies, a China-based company, supplied 70 to 80 percent of the cryptocurrency ASICs in 2017. Its customers typically use "crypto rigs"-multiple ASICs working together-to optimize compute speed. By conservative estimates, BitMain Technologies has a gross margin of 65 to 75 percent and an operating margin of 55 to 65 percent-equivalent to \$3 billion to \$4 billion in 2017. That figure is roughly the same as the profit margin for Nvidia, which has been in business for 20 years longer.

Although most major cryptocurrencies now reward miners with high compute speed, some have taken steps to prevent large mining pools with crypto rigs from dominating the market. For instance, Ethash, the hashing algorithm that Ethereum uses, is designed to be ASIC resistant—and that means miners must fetch random data and compute randomly selected transactions to solve their cryptographic questions. Both activities require frequent access to memory, which ASICs alone won't provide. Ethereum miners primarily rely on a system that utilizes a GPU in combination with memory.

#### Blockchain 2.0: Uncertainty about cryptocurrencies and the emergence of business applications

The Blockchain 2.0 era will likely usher in many changes. The cryptocurrency market could become more diverse if Bitcoin continues to decrease in price, since ICOs may see the situation as an opportunity to stake their claims. Consumers may also begin demonstrating more interest in other established altcoins. For instance, users may come to favor Dash or Litecoin for some transactions, since they offer faster transaction speed than Bitcoin does. Companies and the general public are generally becoming more comfortable with cryptocurrency transactions, which could increase usage rates.<sup>1</sup>

In tandem with these changes, the market for blockchain business applications is heating up as BaaS simplifies implementation. Demand for these applications is expected to be strong, and corporate users could soon outnumber cryptocurrency miners.

Investors are showing continued interest in blockchain, although funding levels have recently declined. Venture-capital funding peaked in 2017 at about \$900 million for both cryptocurrency and business applications, and it will likely still be between \$600 million and \$800 million in 2018. It is unclear whether 2019 will show continued decline, a plateau, or greater investment.

Although it is difficult to make predictions about blockchain, since it is a relatively new technology, we were able to identify several trends in the cryptocurrency and business-application markets

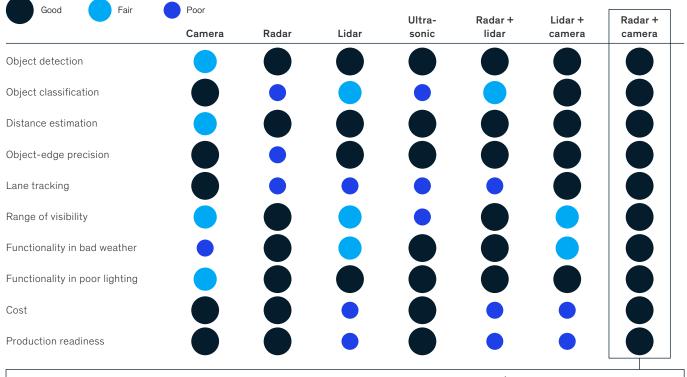

<sup>&</sup>lt;sup>1</sup> Josh Ong, "The branding of cryptocurrency," *Forbes,* March 1, 2018, forbes.com.