Semiconductor wafers are the basis of the integrated circuits so crucial to most of today’s technology. The wafers’ packaging—whether metal, plastic, ceramic, or glass—connects them to their environment and protects them from chemical contamination and damage from light, heat, and impacts. Compared with the front-end process of designing and fabricating wafers, the back-end process of packaging has been undervalued for two reasons: First, it’s still possible to package wafers using old-generation equipment. Second, packaging is mostly done by outsourced semiconductor assembly and test companies (OSATs) that compete largely based on low labor costs, rather than other sources of differentiation.

This model may change with the introduction of advanced packaging, which uses sophisticated technology and aggregates components from various wafers, creating a single electronic device with superior performance. Introduced around 2000, advanced packaging is now gaining significant momentum as the next breakthrough in semiconductor technology.

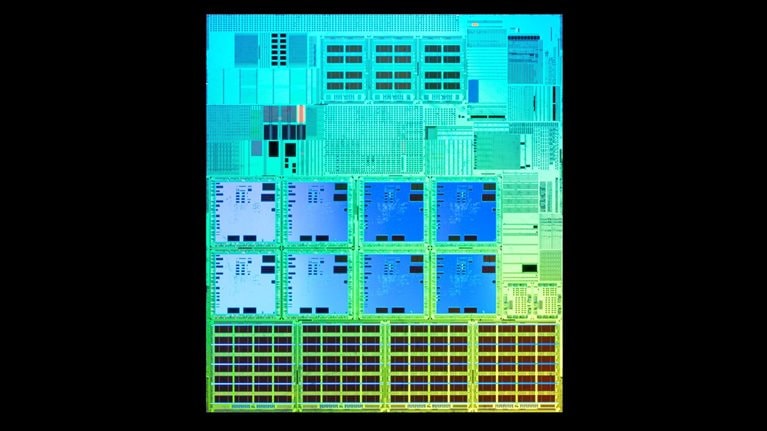

Advanced packaging is helping to meet the demand for semiconductors that run emerging applications now going mainstream—for example, 5G, autonomous vehicles and other Internet of Things technologies, and virtual and augmented reality. These applications require high-performance, low-power chips that can rapidly process massive quantities of data. Despite Moore’s law, which in 1965 posited that the number of transistors on a microchip would double every couple of years, node advancement is now reaching its limits. As a result, technical advances on the front end of chip manufacturing are slowing, and the economically viable maximum size of a die, and thus its performance, are becoming more limited. New approaches in back-end technology that combine multiple chips offer a promising solution. Advanced-packaging techniques that have arisen over the past two decades—including 2.5-D, 3-D, fan-out, and system-on-a-chip (SoC) packaging—promise to fill the void by supplementing the wire-bonding and flip-chip technologies of the previous half century.

Because advanced packaging offers a higher-value opportunity than traditional back-end packaging, major players and fast followers (organizations that imitate competitors’ innovations) are developing and commercializing various forms of the technology to win premium customers. In this article, we describe how the market is evolving and suggest how manufacturers can take advantage of the opportunities becoming available.

Key advanced-packaging technologies

Three major advanced-packaging technologies have become commercially available since 2000, supplementing the two technologies that prevailed during the previous half century (Exhibit 1).

Traditional packaging techniques

Developed in the 1950s and still in use today, wire-bond technology is an interconnection technique that attaches the printed circuit board (PCB) to the die—the silicon square that contains the integrated circuit—using solder balls and thin metal wires. It requires less space than packaged chips and can connect relatively distant points, but it can fail in high temperatures, high humidity, and temperature cycling, and each bond must be formed sequentially, which adds complexity and can slow manufacturing. The wire-bonding market is expected to be valued at about $16 billion by 2031, with a CAGR of 2.9 percent.1

The first major evolution in packaging technology came in the mid-1990s with flip chips, which use a face-down die, the entire surface area of which is used for interconnection through solder “bumps” that bond the PCB with the die. This results in a smaller form factor, or hardware size, and a higher signal-propagation rate—that is, faster movement of signals from the transmitter to the receiver. Flip-chip packaging is the most common and lowest-cost technology currently in use, mainly for central processing units, smartphones, and radio-frequency system-in-package solutions. Flip chips allow for smaller assembly and can handle higher temperatures, but they must be mounted on very flat surfaces and are not easy to replace. The current flip-chip market is around $27 billion, with a projected CAGR of 6.3 percent, which should bring it to $45 billion by 2030.2

Wafer-level packaging

While traditional packaging “dices” the silicon wafer into individual chips first and then attaches the chips to the PCB and builds the electrical connections, wafer-level packaging makes the electrical connections and molding at the wafer level, then dices the chips using a laser. The greatest difference between wafer-level chip-scale packaging (WLCSP) and flip chips in terms of chip configuration is that WLCSPs have no substrate between the die and the PCB. Instead, redistribution layers (RDLs) replace the substrate, leading to a smaller package and enhanced thermal conduction.

Wafer-level packaging is divided into two types: fan-in and fan-out. In fan-in wafer-level packaging, used mainly for low-end mobile phones that require rudimentary technology, the RDLs are routed toward the center of the die. In the fan-out version, which was introduced in 2007, the RDL and solder balls exceed the size of the die, so the chip can have more inputs and outputs while maintaining a thin profile.3 Fan-out packaging comes in three types: core, high density, and ultrahigh density. Core, which is used mostly for automotive and network applications that don’t require high-end technology—such as radio frequency and infotainment chips—accounts for less than 20 percent of the almost $1.5 billion fan-out packaging market. High and ultrahigh density are mostly used for mobile applications and are expected to expand to some network and high-performance computing applications. The world’s largest maker of WLCSPs is the Taiwan Semiconductor Manufacturing Company (TSMC).

The past decade saw the development of stacked WLCSP, which allows for multiple integrated circuits in the same package and is used for both heterogeneous bonding, which integrates logic and memory chips, and memory-chip stacking. In 2.5-D stacking, two or more chips are laid side by side with an interposer connecting one die to another. There are several categories of 2.5-D stacking, based on the kind of interposer it uses:

- Silicon interposers are the only type that requires TSV, or through-silicon via—a vertical electrical connection that passes through the silicon die or wafer. Silicon interposers use a stable technology that has been on the market for more than ten years, but the cost of silicon is high and requires front-end technology and manufacturing capability. TSMC’s CoWoS-S (chip on wafer on substrate) dominates the market.

- Silicon bridges are relatively new. Because they use smaller amounts of silicon than traditional silicon interposers, they are thinner, which reduces power consumption and increases design flexibility. Their advantage over traditional silicon interposers is that they can enable more advanced system-level integration, so they are used for high-performance computing (HPC) such as AI. Representative technologies include Intel’s EMIB (embedded multi-die interconnect bridge) and TSMC’s CoWoS-L.

- Redistribution layers can also function as interposers. The greatest strength of this technology is that the photolithography process that creates RDLs allows for fine patterning, which improves speed gain and heat dissipation. TSMC’s CoWoS-R (chip-on-wafer-on-substrate RDL) is set to begin mass-volume production.

- Glass is also rising as a next-generation material for interposers. It offers low cost and low power loss in high-frequency bandwidths, but it may not be marketable for some time.

In 3-D stacking, multiple chips are placed face down on top of one another, with or without an interposer. There are two main types of 3-D stacking. The most common type is TSV with micro-bumps (µ-bumps). The newer alternative, bumpless hybrid bonding, forms interconnections using a dielectric bond and embedded metal; it is just being explored by memory players.

How will the market evolve?

The advanced-packaging market is driven by the end applications of its various technologies (Exhibit 2). Since the mid-2010s, fan-out wafer-level packaging has dominated, with about 60 percent market share. Fan-out packaging is cheaper than stacking and is engineered for high heat resistance and a small form factor. These attributes make it appropriate for mobile applications, which are likely to generate most of its demand.

Apple uses fan-out advanced packaging for its application processors, graphic chips, and 5G and 6G modem chips. It is the largest user of the technology, consuming most of the volume produced by TSMC. Other top fabless players—that is, companies that design and sell hardware and chips but outsource their manufacture—are also using fan-out technology in mass-produced chips.

Most of the growth in HPC and network applications is likely to come from AI chips, edge computing, and network chips in consumer devices, which require the small form factor and affordable cost that fan-out packaging can offer.

The most likely driver of growth in 2.5-D stacking could be HPC applications, which are in high demand for data centers. Although less than 20 percent of data-center capacity used 2.5-D stacking in 2022, the rate could increase to 50 percent in the next five years. For mobile applications, 2.5-D packaging is considered too costly, but this may change with the arrival of the next generation, which will feature less expensive silicon bridges, RDLs, and glass interposers.

For 3-D packaging, memory—the dominant application for 3-D stacking—and SoC use are expected to grow at a CAGR of roughly 30 percent. Increasingly, 3-D stacked memory is being incorporated with logic chips for high-performance products that require high bandwidth, including high-bandwidth memory (HBM) and processing in memory with HBM (PIM-HBM). Substantial demand for 3-D stacked memory will likely come from data-center servers, which require high capacity and high speed, and graphics accelerators and network devices, which require the maximum possible bandwidth for memory and processing.

HPC systems, specifically CPUs, will drive demand for 3-D SoC chips. Major players started adopting hybrid bonding in 2022, and fast followers may join the market soon. OSATs, lower-tier foundries, and integrated device manufacturers (IDMs) are unlikely to enter the market, given the high technology barrier.

Key market-winning capabilities

Market growth relies heavily on end customers, such as automotive OEMs and home appliance manufacturers. More end customers are seeking advanced-packaging providers because of the growing need for fast, reliable computing for applications such as autonomous vehicles. For semiconductor manufacturers—especially logic IDMs and foundries—advanced packaging could be a key selling point.

To acquire and retain high-value fabless customers, manufacturers need to be comfortable codeveloping advanced-packaging solutions. While fabless players take full ownership of the chip-planning process before at-scale production begins, there is room for manufacturers to add value. Joint development often occurs during the chip-architecture design stage and initial shuttle runs for design validation (Exhibit 3). The need for such cooperation is expected to increase because of the demand for higher-performance chips and the increased complexity of chip designs created by packaging.

In 2016, TSMC released innovative integrated fan-out (InFO) wafer-level systems, mainly for wireless applications, in close collaboration with its lead customer. More recently, derivatives of that, such as InFO AiP (antenna in package) and InFO PoP (package on package), have been released to expand into other applications for networking and HPC.

Fast followers may have a hard time catching up with market leaders, because huge technology investments would be required to assure customers of the volume to support products. In addition, although fast followers may have R&D-level packaging technology for fan-out and 2.5-D, they have little or no production experience, which is essential for high production yield. To overcome this, packaging players would need to acquire anchor customers from the initial stages of development. Positioning their companies as willing to help manufacture products for advanced packaging from the design stage would be key to acquiring customers.

Advanced packaging requires changes in the architecture of end-user software and hardware, so packaging design should be considered during the initial architecture stage, when support from back-end providers can lower the burden of adopting advanced packaging. Once a customer selects an advanced-packaging vendor, it will likely commit to that vendor for future projects as well.

To acquire design capabilities, companies can partner with or invest in a design house. Design houses play a critical role across the entire chip-making process, from intellectual-property (IP) development to design and production. Additionally, owning an IP pool can help customers meet their design needs quickly and allow them to avoid redundant designs and resources. Design houses should be able to offer front- and back-end services. Front-end services include register-transfer-level design and high-level description of the functions required; back-end design includes logic testing and place and route.

Another potentially important value proposition for the chip manufacturer is securing design capabilities and providing turnkey solutions—from design to wafer manufacturing, packaging, and testing. This type of offering provides customers with a one-stop shop.

In terms of manufacturing, the two key technological capabilities manufacturers need to master for 2.5-D and 3-D packaging are, respectively, interposers and hybrid bonding. For 2.5-D, manufacturers must be able to handle emerging interposer solutions using novel materials and manufacturing methodologies, including silicon, RDL, and glass. For 3-D, the latest technology, hybrid bonding, requires chemical mechanical planarization to polish various substances with equal flatness and prevent dishing, as well as high interconnect accuracy through disk-to-wafer capabilities in both equipment and know-how.

Implications for manufacturers

Key players in advanced packaging include logic and memory IDMs, foundries with leading or mature node capabilities, and OSATs. Exhibit 4 shows the capabilities currently handled by first movers and fast followers.

First movers

First movers have entered the market and are in mass-volume production based on their logic-packaging capabilities. They are actively developing use cases with existing customers and applying cutting-edge advanced-packaging technologies. While these major players are advanced in R&D and manufacturing, they may seek partnerships with followers to stabilize volume as they face rapidly expanding demand.

Fast followers

Many fast followers are striving to take a share of the advanced-packaging market but have not mastered the design or manufacturing capabilities or built a sufficient customer base, especially for high-end solutions.

Foundries that have mature node capability but lack advanced packaging could benefit substantially from finding synergies within their current product portfolios. While advanced logic chips with nodes smaller than ten nanometers have the greatest need for advanced packaging, it is critical for fast followers to find opportunities to capture the mature-node market. Some of the areas where advanced packaging can be adapted to enhance the performance of mature-node legacy chips are radio-frequency transceiver chips for network applications, advanced driver-assist systems (ADAS), and infotainment chips for automotive applications.

Another option is to partner with logic providers to develop design and manufacturing solutions for specific applications that use both mature and leading-edge nodes. The feasibility of this tactic would largely depend on the end-application demand and logic providers’ needs.

OSATs

OSATs’ capabilities in the high-end advanced-packaging market are limited. Rather than trying to compete directly with high-end solutions, they can offer comparatively low-end solutions or seek to collaborate in certain value-chain areas with players capable of high-end advanced packaging. Leading OSATs are actively investing to expand the range of advanced packaging they offer. Some can already handle core and HD-level fan-out packaging, but 2.5-D and 3-D stacking mainly remain in R&D.

Another option for OSATs is to partner with players capable of 2.5-D and 3-D stacking. While these partners work on core processes—including through-silicon via, RDL lithography, and hybrid bonding—the OSATs could offer solutions for the mid- to back-end processes, including wafer thinning and bumping.

Although foundries and IDMs are developing advanced-packaging capabilities, they will likely use advanced packaging only to attract high-end customers that require state-of-the-art technology and, therefore, will not disrupt the entire OSAT business. They are not expected to expand into core and fan-out advanced packaging, given the significant differences in operating margin compared with front-end manufacturing, though they may make the leap into more profitable advanced 2.5-D or 3-D packaging.

Memory IDMs

Logic capability is essential for advanced packaging, but 3-D stacking technology can still present opportunities for memory IDMs, as top players are using it to enhance performance in memory chips that include basic-level logic chips. IDM players can also differentiate themselves by using the technology to customize memory for key clients’ advanced-packaging chips.

Another scenario for memory IDMs is to develop logic capabilities, particularly in design or manufacturing, to enable synergies with advanced packaging. This would, however, require substantial investment and a risky leap across the value chain.

The advent of advanced packaging has changed the competitive landscape for chip manufacturers. Packaging is no longer a commodity process, and the majors have moved first to make advanced packaging a strategic part of their offerings. Other manufacturers risk being commoditized if they don’t find a way to incorporate advanced packaging into their strategies and offerings. The advanced-packaging market offers many disruptive opportunities, as well as challenges that will likely go beyond business as usual.